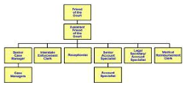

Dr. J. Greg Nash, CTO

Experience

Dr. Nash is president of Centar and is responsible for business planning and technical development. He has focused company efforts on developing intellectual property for use in FPGA and ASIC-based embedded signal processing circuitry and on building CAD tools that can automatically generate optimal versions of these circuits. At of Centar he has been successful in obtaining several Department of Defense (DARPA and BMDO) and NSF SBIR Phase I and II contracts to support these goals. The products and tools described here are in part derived from these contracts.

Dr. Nash is president of Centar and is responsible for business planning and technical development. He has focused company efforts on developing intellectual property for use in FPGA and ASIC-based embedded signal processing circuitry and on building CAD tools that can automatically generate optimal versions of these circuits. At of Centar he has been successful in obtaining several Department of Defense (DARPA and BMDO) and NSF SBIR Phase I and II contracts to support these goals. The products and tools described here are in part derived from these contracts.

While at Hughes Research Laboratories he was in charge of a group developing parallel algorithms, architectures and prototype computers for Hughes embedded military signal and image processing systems. He designed and developed the Systolic/Cellular Processor later pursued at Hughes (now Raytheon) Radar Systems Division for use in airborne radar systems. The prototype machine contained a 16×16 array of custom VLSI 32-bit ASICs and was designed to support efficient computation of algorithms from FFTs to complex linear algebraic operations. He was also responsible for the design and development of the Image Understanding Architecture, an application specific, heterogeneous, associative, massively parallel processor intended to support the complete range of 2-D sensor processing requirements. The prototype was a 16 board system containing a 64×64 array of custom single-bit associative processors and an 8×8 array of TI C25 DSP processors. Dr. Nash has been Principle Investigator on many contracts including several from NSF, DARPA, NOSC and Rome Labs. At Hughes Research Laboratories he received two best paper awards and the Hughes Group Patent award. He also has nine issued patents.

Publications

Dr. Nash has published over 80 articles (mainly conference proceedings and journal articles) primarily relating to parallel algorithms and architectures for image and signal processing.

Professional Activities

Dr. Nash has been active professionally, serving as Chairman of the IEEE VLSI Signal Processing Committee from 1986 to 1988, editor of the J. of VLSI Signal Processing and on the organizational committees for more 10 signal/image processing workshops. He is presently a Senior member of the IEEE.

Education

B.S.E., Princeton University, 1968

M.S., Electrical Engineering, UCLA, 1970

Ph.D., Electrical Engineering, UCLA, 1974.

Employment

1994-present: Centar LLC

1975-1994: Hughes Research Laboratories (HRL)